## Development of CoRDIA: an imager for Diffraction-Limited Synchrotron Rings and Continuous-Wave Free Electron Lasers

on behalf of the CoRDIA collaboration

#### Acknowledgements

## CoRDIA

Nik hef

unec

- the team ( A. Klujev, S. Lange, T. Laurus, D. Pennicard, U. Trunk, C.B. Wunderer, H. Krueger and H. Graafsma)

- NIKHEF (particularly V. Gromov and A. Vitkovskiy), for allowing us to use a version of the PCS-GWT circuit

- CERN and the RD53 collaboration, for allowing us the reuse of CMOS IO pads and SOFIC ESD structures in our design

- Europractice, IMEC and CERN for their MPW and design tool support

- the Caribou collaboration, for providing us with a versatile system for prototype testing

- Motivation

- Overall architecture

- Development plan

- Prototypes

- Test results

- Summary

#### current imager types in photon science

##

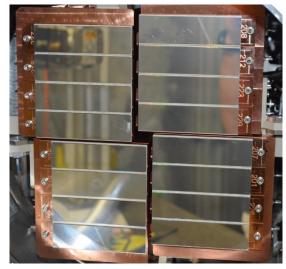

#### imager example for SR: LAMBDA

- Up to 10 megapixel (55 μm pixel size)

- 2 kHz frame rate (continuous)

or MM-PAD-1  $\rightarrow$  2.1

1.1kHz →10 kHz (continuous)

or CITIUS

• 17.4 kHz (continuous)

#### for high-repetition rate FEL: AGIPD

- 1 megapixel (200µm pixels),

4 megapixel in development

- 4.5 MHz burst imaging (internal storage: 352 images)

or LPD (500µm, 500img) or DSSC (hexag, Ø≈230µm, 800img)

4.5 MHz burst imaging (internal storage) 4

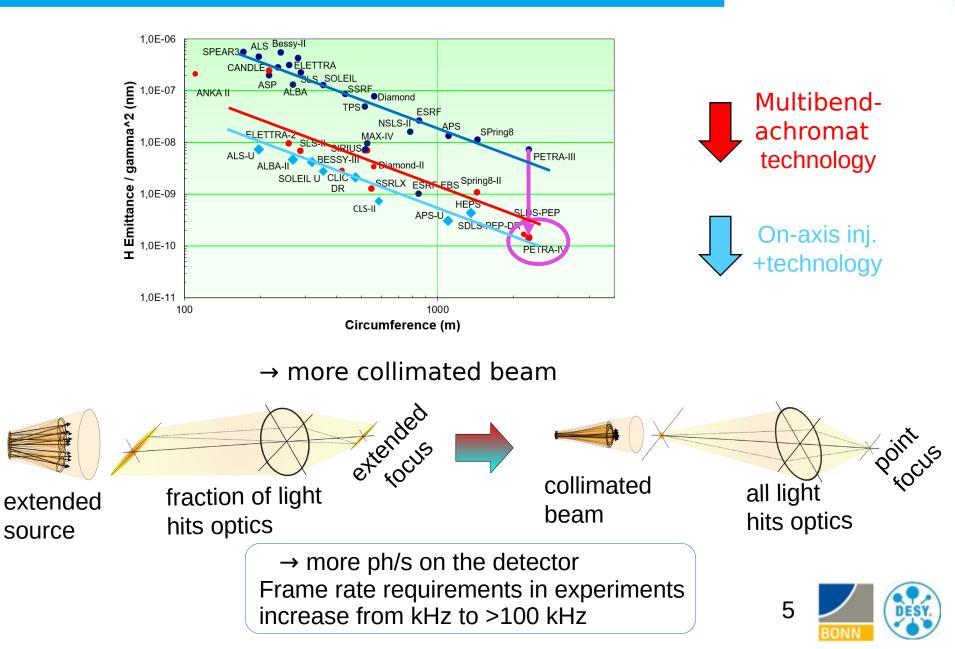

#### SR: 3<sup>rd</sup> → 4<sup>th</sup> gen (diffraction limited)

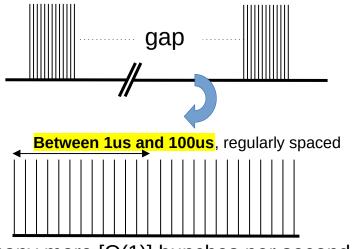

#### **FEL: reducing gaps / elongating trains**

#### coming source upgrades

##

# PETRA-IV: Upgrade to diffraction limited ring (~2030)

PETRA-III electron bunch PETRA-IV electron bunch

- x100-1000 in brilliance, coherent flux

- Frame rate req. in experiments: from kHz to <a>>100 kHz</a> (continuous) readout

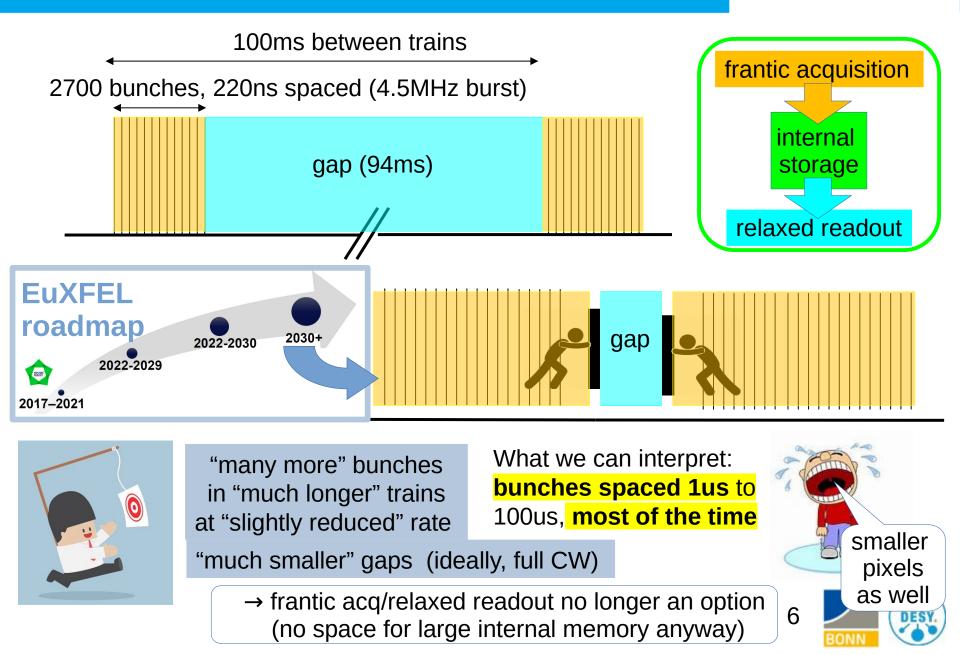

# European XFEL: CW mode operation (20??)

many more [O(1)] bunches per second no gap for burst-readout of internal storage

common need for: • continuous readout • > 100kHz frame rate

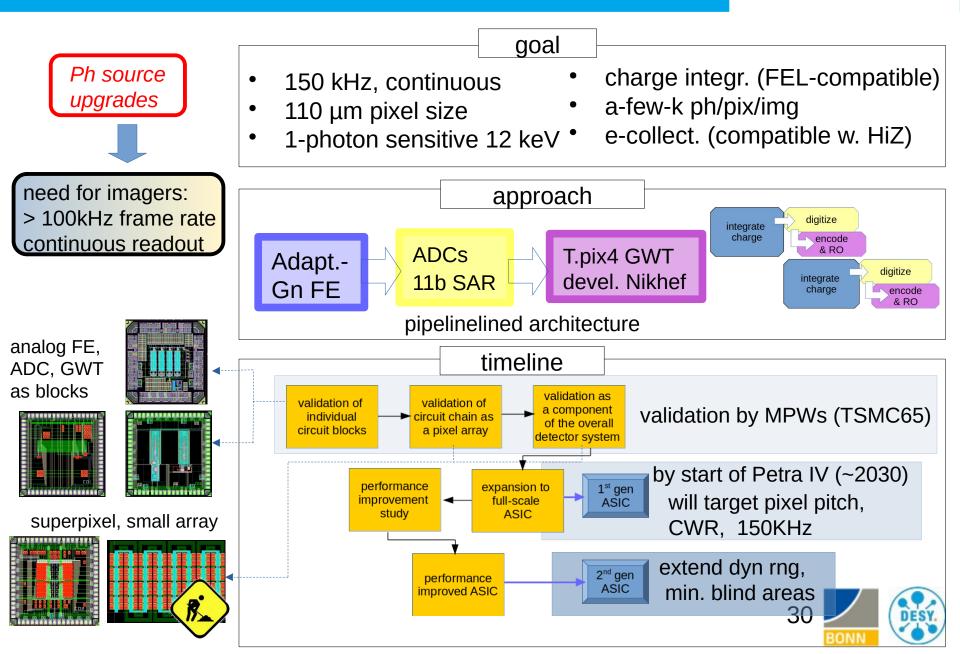

#### **CO**ntinuous Readout Digitising Imager Array

#### our goals

- 150 kHz, continuous

- charge-integrating (FEL-compatible)

- ~110 µm pixel size •

- 1-photon sens. 12 keV

- a-few-k ph/pix/img (aiming 10k, not there yet)

**CORDIA**ASIC

eV • compatible with High-Z

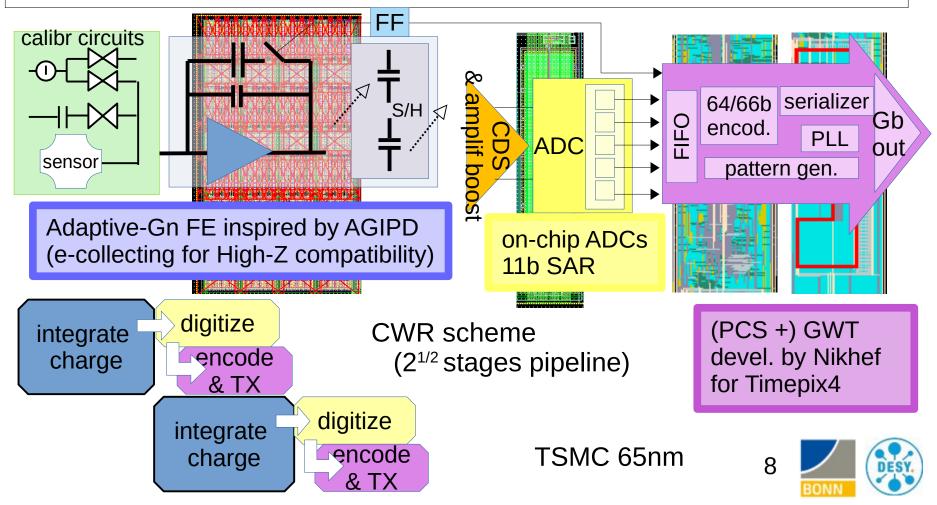

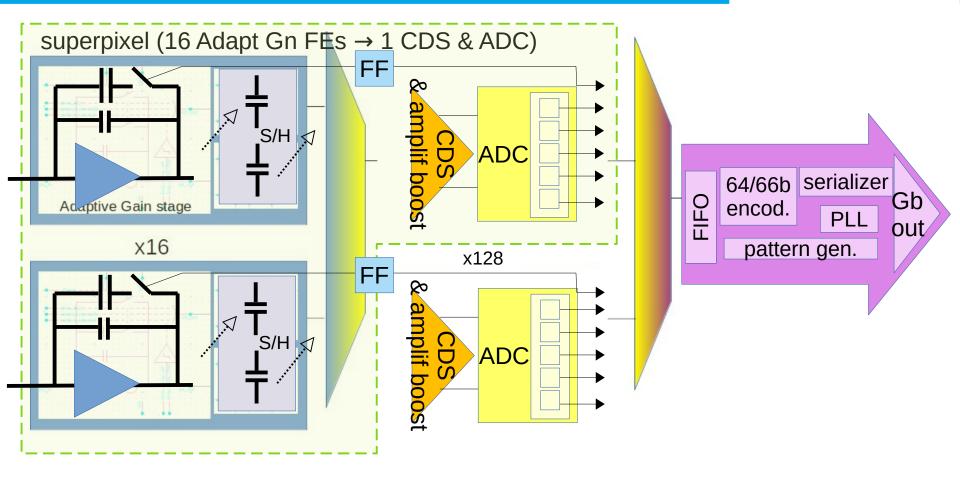

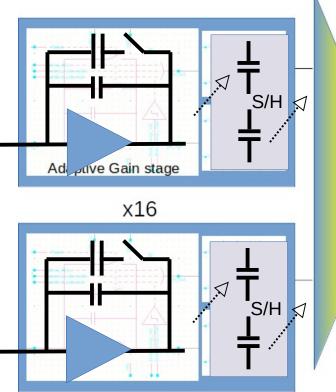

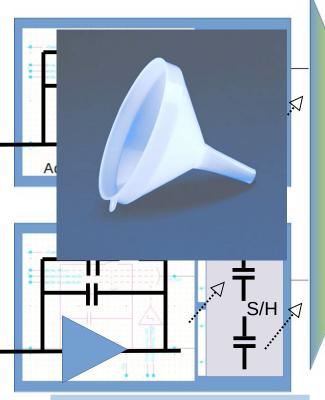

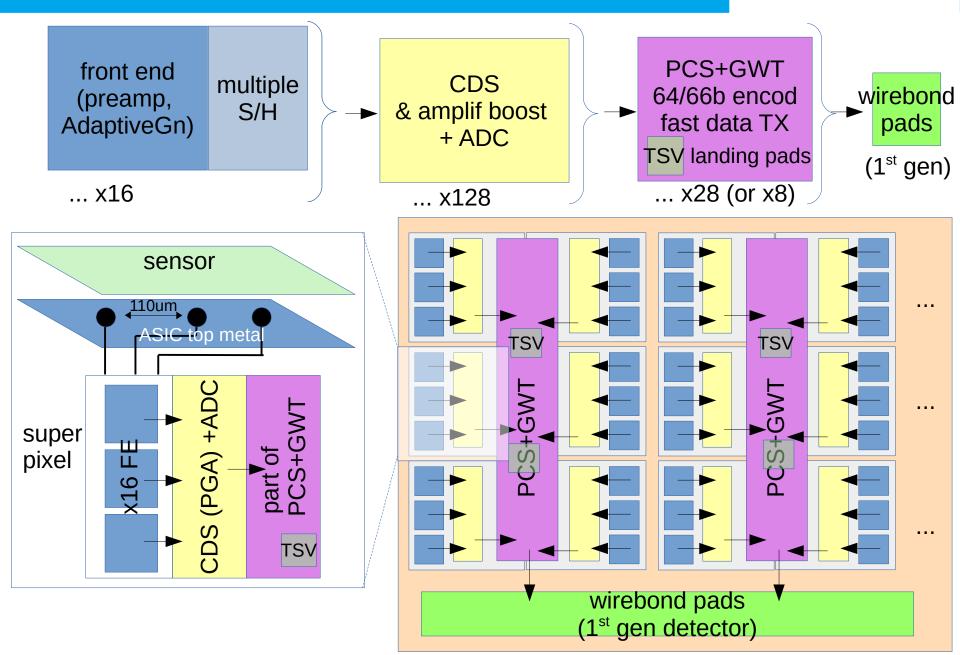

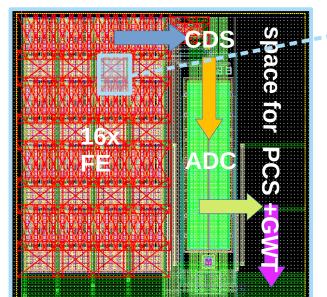

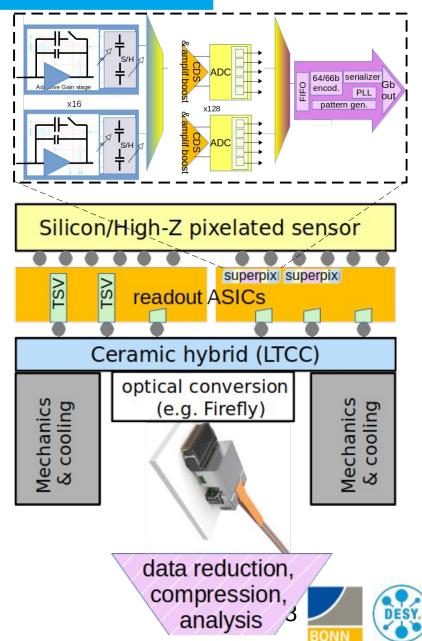

## **CORDIA**<sub>ASIC</sub> structure

## **CORDIA**ASIC

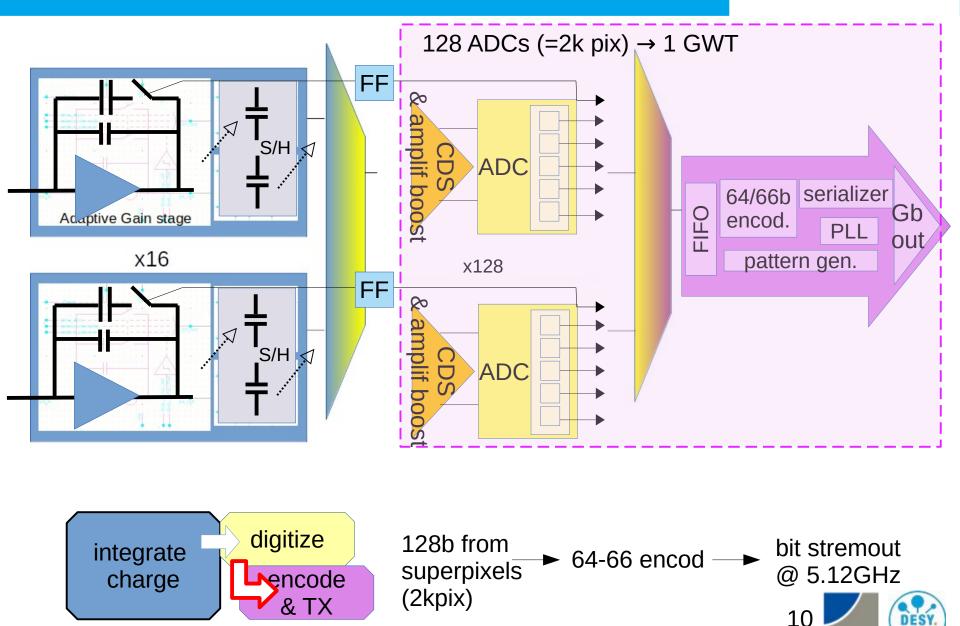

sequential digitization (11b) + Gn bit of the former image per 16 pixels (charge stored in S/H cells)

###

BONN

## CORDIA<sub>ASIC</sub> structure

### **CORDIA**<sub>ASIC</sub> structure

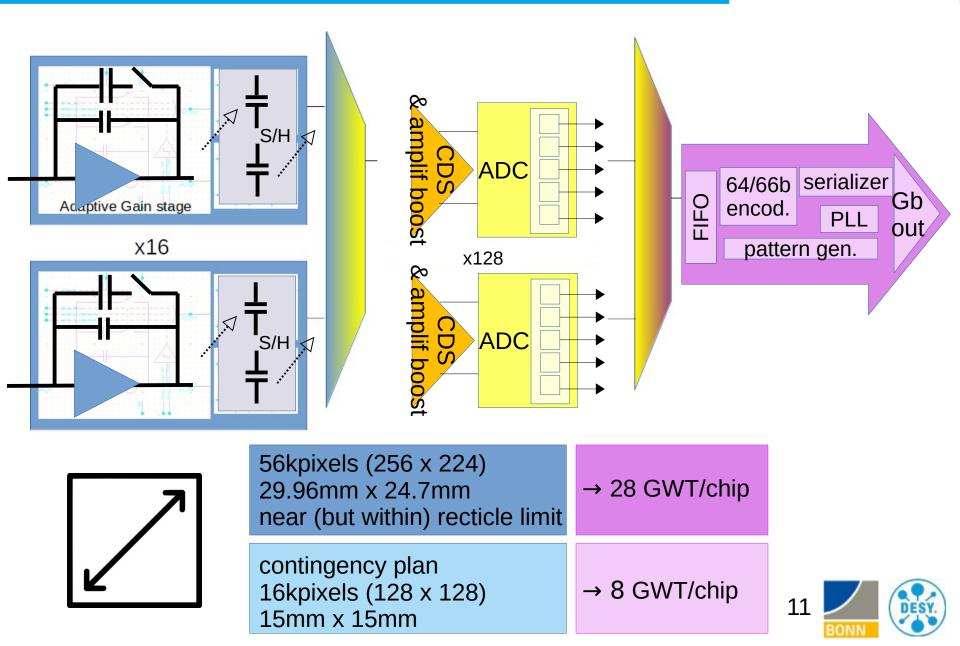

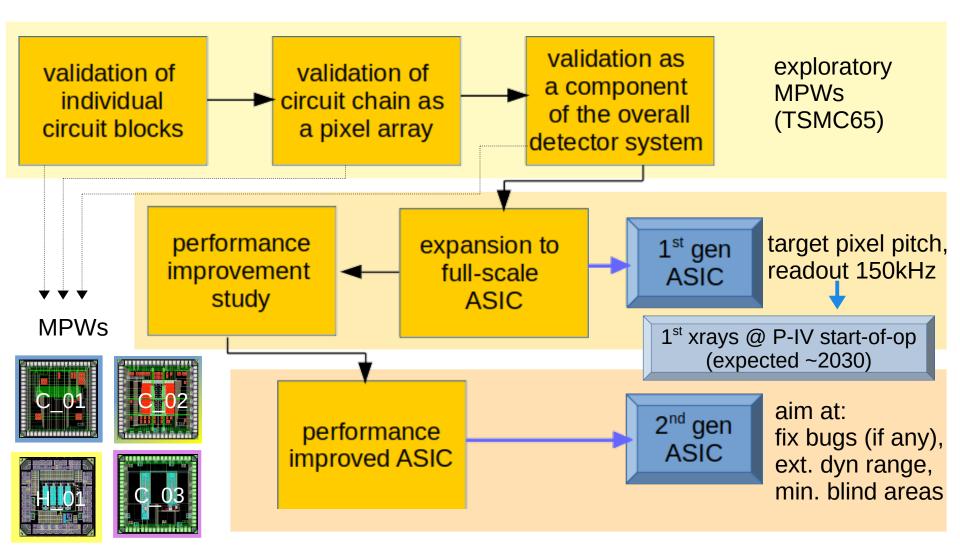

our plan

#### **MPWs**

##

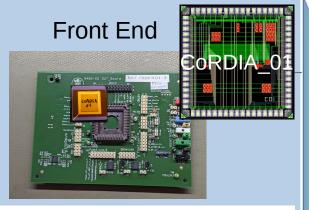

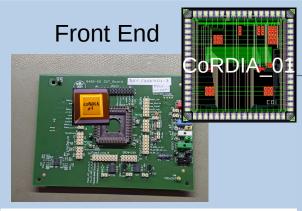

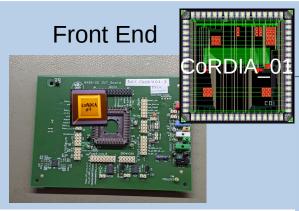

2021: CoRDIA\_01 Designed, produced, tested. Used to validate analog circuit blocks as at the

expected frame rate

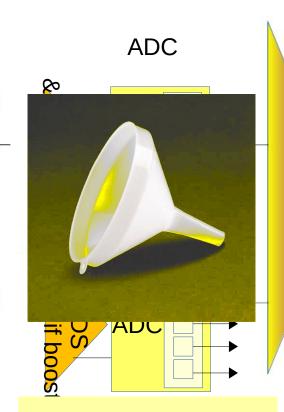

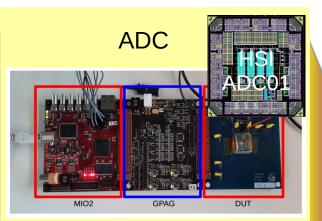

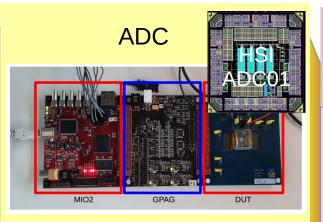

#### 2021: HSI\_ADC01 Designed, produced, tested.

Used to confirm image sampling capability at the expected frame rate

2022-2023: CoRDIA\_02 Designed, produced. Currently under test. Used to validate pipeline signal-processing and evaluate performances.

2023: CoRDIA\_03 Designed, produced, being wire-bonded now Test expected summer. Will be used to validate the PCS+GWT circuit, optimized to CoRDIA.

CoRDIA\_04 prototype-to-come: small-sized pixel array (~2kpixels, design in progress, expected after C03 test) floorplanning as a meandering structure to emulate full-size chip size "column" (to estimate eventual drops before fullsize chip engineering run)

## **CORDIA**<sub>ASIC</sub> expectations

## **CORDIA**ASIC

#### Front End

## **CoRDIA**<sub>ASIC</sub> expectations

##

#### Front End

Original spec >100kHz PetralV revol. rate 133kHz Users are greedy kids

$\rightarrow$  FE design, tested (DESY)

>150 kframe/s

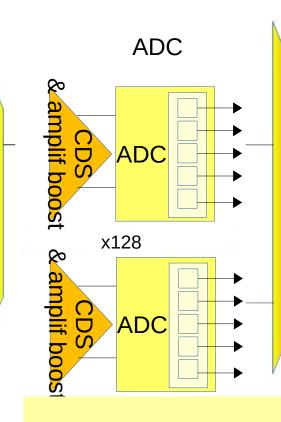

1 ADC serves 16 FEs, so it needs to operate at least at 150k x 16= 2.4MS/s

$\frac{\rightarrow \text{ADC tested (UniBonn)}}{2.5 MS/s} \stackrel{\circ}{>} 150 \, k frame/s$

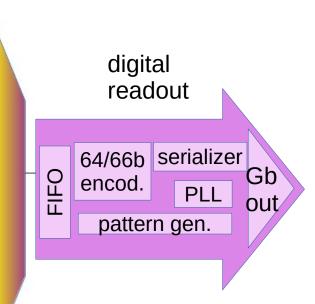

11 bits, + Gn bit └─▶ < 2Bytes/pix 16\*128= 2kpixel / GWT 64-to-66bit encoding

$\rightarrow$  GWT tested (NIKHEF)

5.12 Gb/s 12~16b\* 2k pixels \*66/64 >150 kframe/s

#### checking the puzzle pieces...

## **CORDIA**ASIC

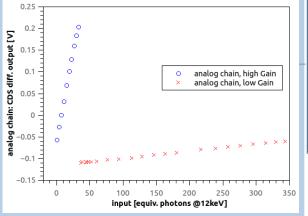

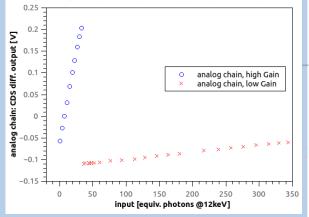

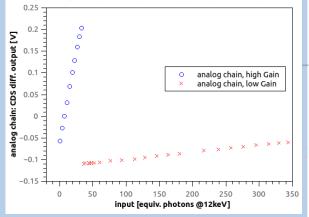

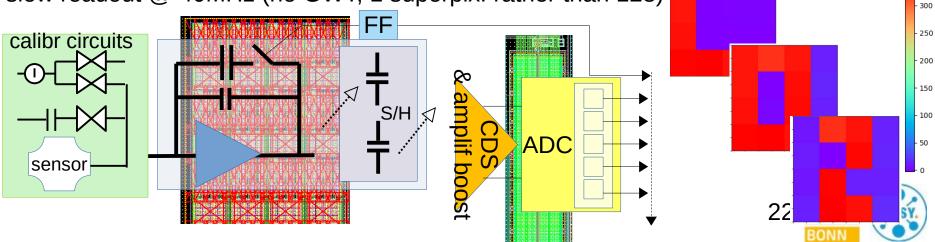

analog chain (preamplifier + S/H + CDS), Adaptive Gain operation

Adaptive Gain circuit tested by calibr. source (pulsed capacitor) @ expected frame rate

1 ADC serves 16 FEs, so it needs to operate at least at 150k x 16= 2.4MS/s

$\frac{\rightarrow \text{ADC tested (UniBonn)}}{2.5 MS/s} \stackrel{\circ}{>} 150 \, k frame/s$

11 bits, + Gn bit └─▶ < 2Bytes/pix 16\*128= 2kpixel / GWT 64-to-66bit encoding

$\rightarrow$  GWT tested (NIKHEF)

5.12 Gb/s 12~16b\* 2k pixels \*66/64 >150 kframe/s

#### checking the puzzle pieces...

## **CORDIA**ASIC

analog chain (preamplifier + S/H + CDS), Adaptive Gain operation

Adaptive Gain circuit tested by calibr. source (pulsed capacitor) @ expected frame rate

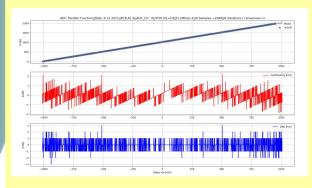

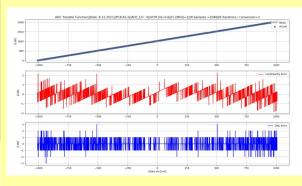

11-bit SAR developed, tested by UniBonn. DNL , INL test suggests >10ENOBs @ expected frame rate digital readout

11 bits, + Gn bit → < 2Bytes/pix 16\*128= 2kpixel / GWT 64-to-66bit encoding

$\rightarrow$  GWT tested (NIKHEF)

5.12 *Gb/s*

12~16*b*\* 2*k* pixels \*66/64

>150 kframe / s

#### checking the puzzle pieces...

##

analog chain (preamplifier + S/H + CDS), Adaptive Gain operation

Adaptive Gain circuit tested by calibr. source (pulsed capacitor) @ expected frame rate

11-bit SAR developed, tested by UniBonn. DNL , INL test suggests >10ENOBs @ expected frame rate

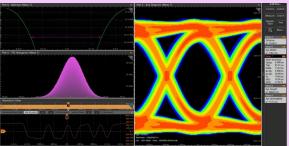

#### PCS+GWT lazy-person approach: reuse Timepix4 solution

X. Llopart on behalf of the Medipix4 collaboration 11 Feb 2022, CERN seminar

prelim: NIKHEF & Medipix collab.: good eye diagram @ 5.12 Gb/s.

adapted circuit perform.

to be confirmed on CoRDIA prototype (being wirebonded)

#### ...looking at the picture on the box...

#### ... combining (some of) the puzzle pieces

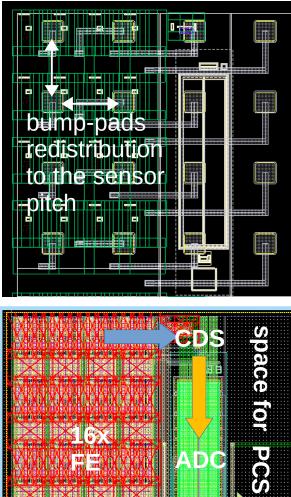

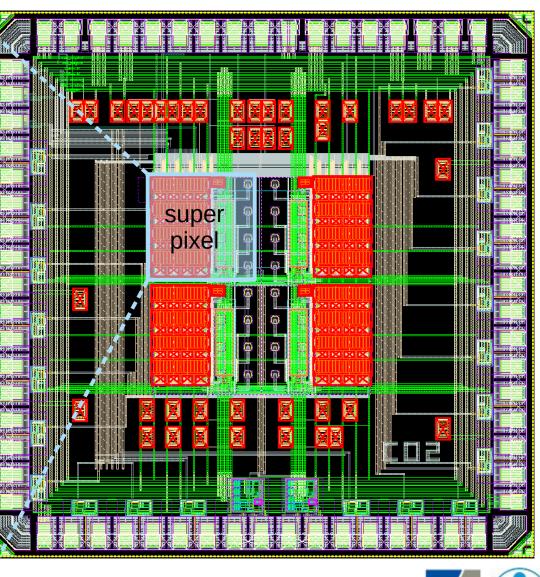

## **CORDIA**ASIC

pad redistrib on top metal

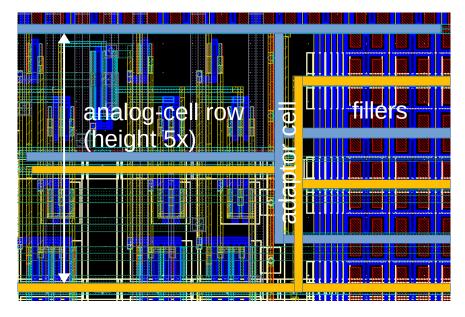

#### ... made of smaller puzzle pieces

##

effort to design analog blocks in a standard-cell fashion for ease of placement and reuse and compatibility to existing cells (e.g. fillers)

#### do they fit together?

## **CORDIA**ASIC

pattern  $[\Delta ADU]$

#### test using Caribou setup

versatile testbox system, providing cntrl, bias & DAQ

see: T. Vanat et al. PoS TWEPP2019 (2020) 100

charge injection in selected pixels using calibration circuits (pulsed-C, Isource) image acquisition @ operational speed (150kfr/s) slow readout @ 40MHz (no GWT, 1 superpix. rather than 128)

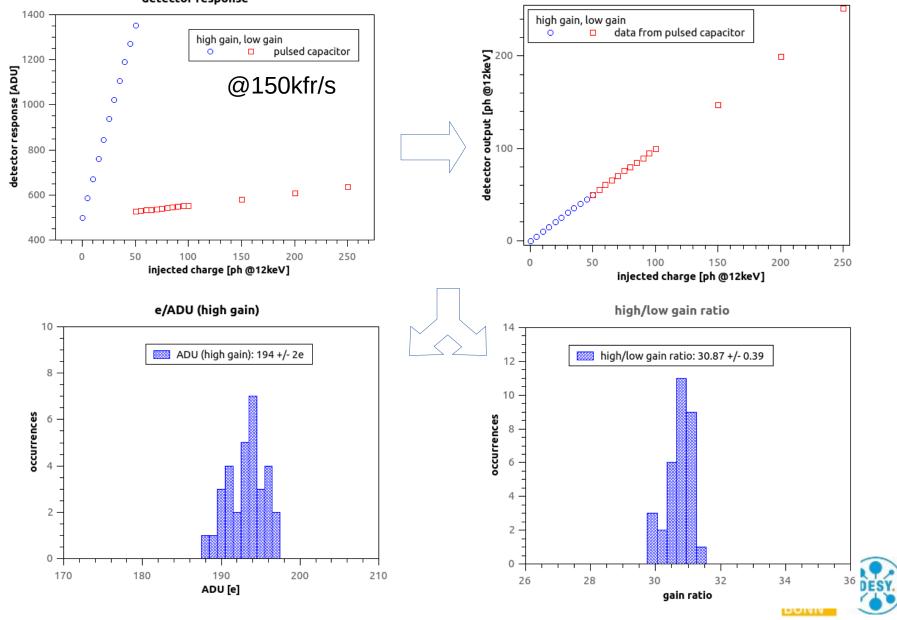

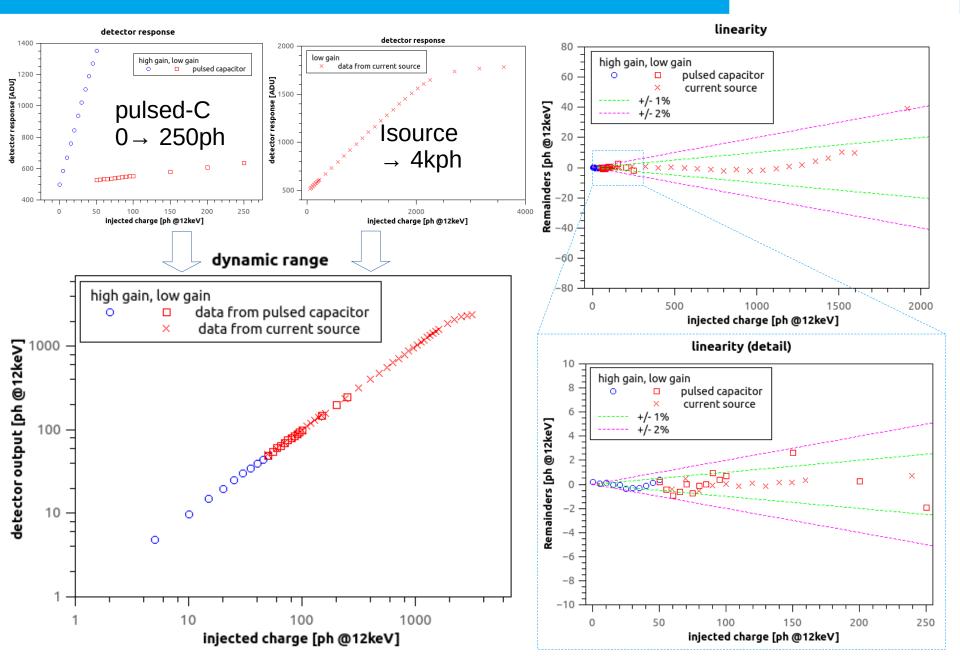

#### pulsed-C $\rightarrow$ Ad-Gn reconstruction, e/ADU est. CoRDIA<sub>ASIC</sub>

detector response

reconstructed detector response

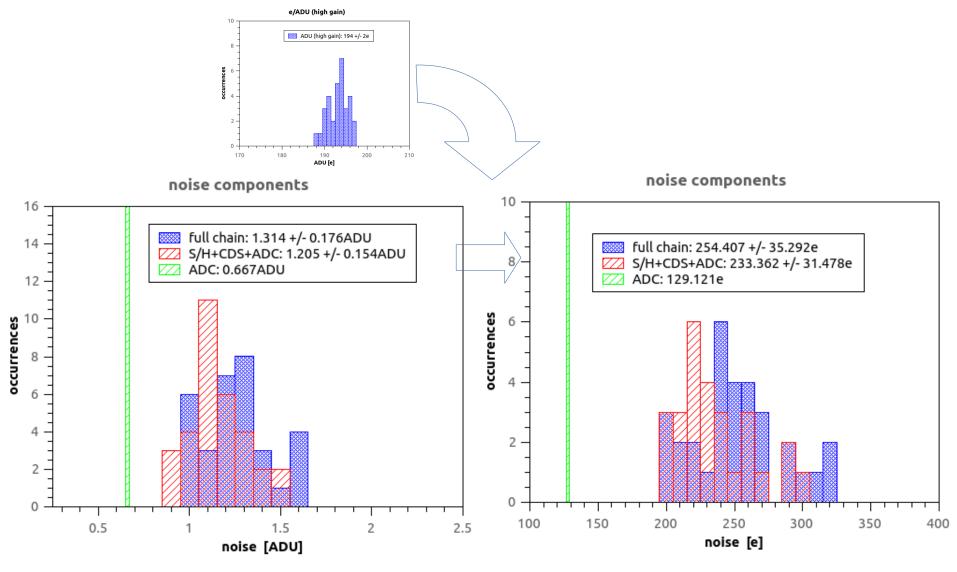

#### dark noise estimation

#### dynamic range estimation

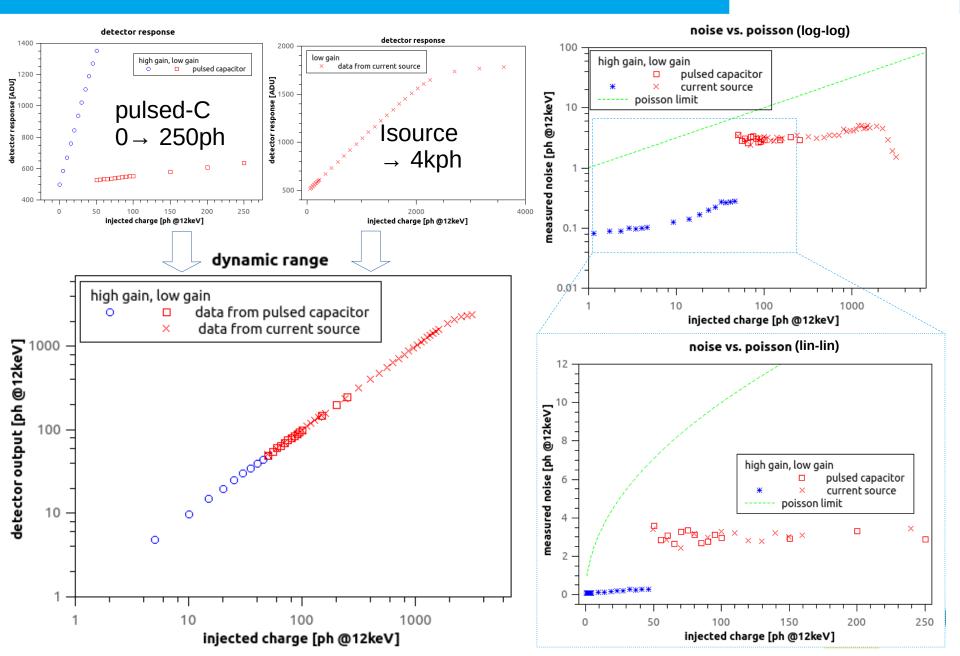

#### noise vs. poisson

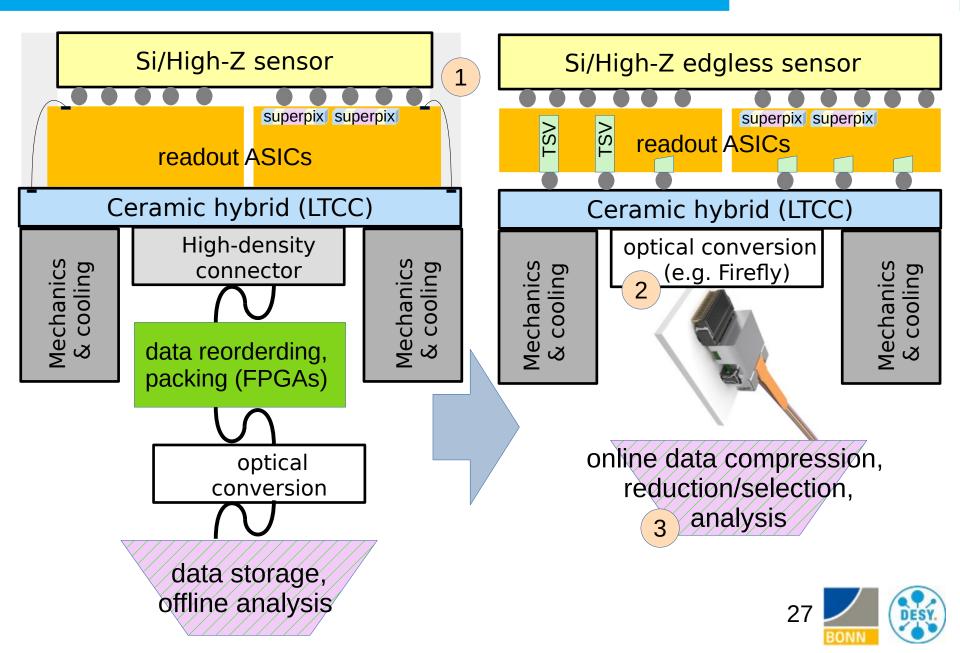

#### a glimpse of the bigger picture

## CoRDIA

#### but beware of the ...

## CoRDIA

Even when used at reduced speed, produces a considerable data output:

1Mpix(min. size palatable by users)x 12bit/pix(min discr. 11bit ADC + Gn)x 133kframe/s(PetralV bunch rate)x 66/64(encoding for GWT)

> 200GBytes/s (>1.6Tb/s)

addressed on silicon: pipelined architecture, on-chip ADCs, high-speed drivers

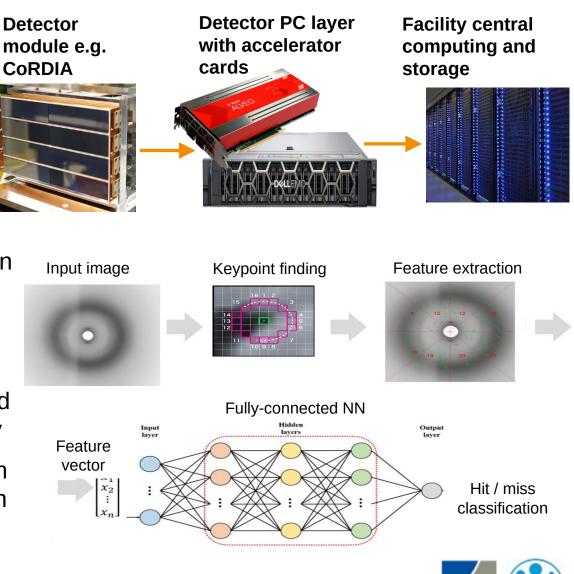

out-of-Silicon: considering Xilinx Alveo acceleration cards

#### **Data reduction**

## CoRDIA

29

- Soal use accelerator cards with built-in network links to receive, buffer and process detector data

- Experimented with Xilinx Alveo FPGA card with 2x100 GBE

- Compared performance for bad image rejection between CPU, GPU and FPGA

- > Developed machine-learningbased methods for rejecting bad images in serial crystallography

- E.g. extracting features from images with computer vision techniques, then classifying with neural network (MLP)

multilayer perceptron, a feedforward artificial neural network

#### **CoRDIA** in a nutshell

##