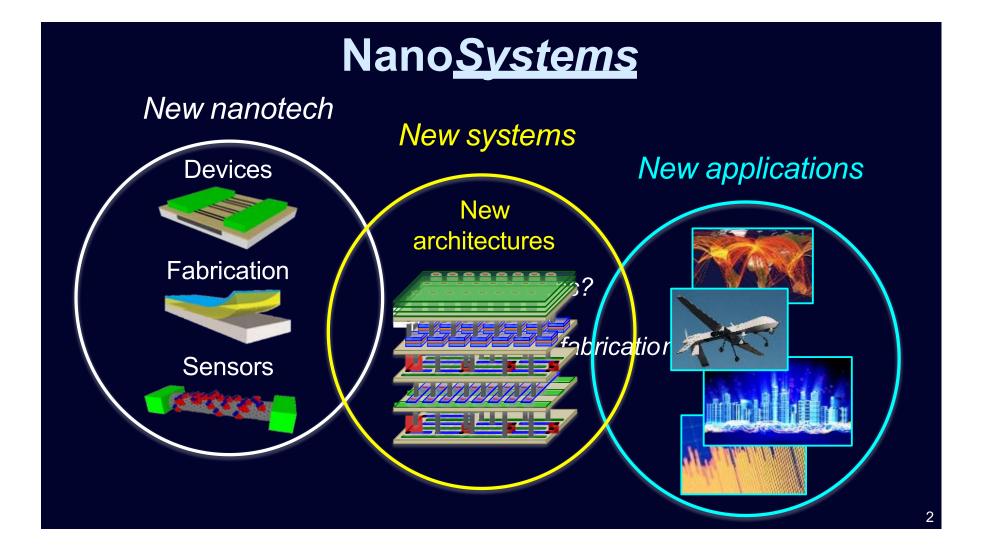

# NanoSystems The N3XT 1,000×

### Subhasish Mitra

Department of EE & Department of CS Stanford University

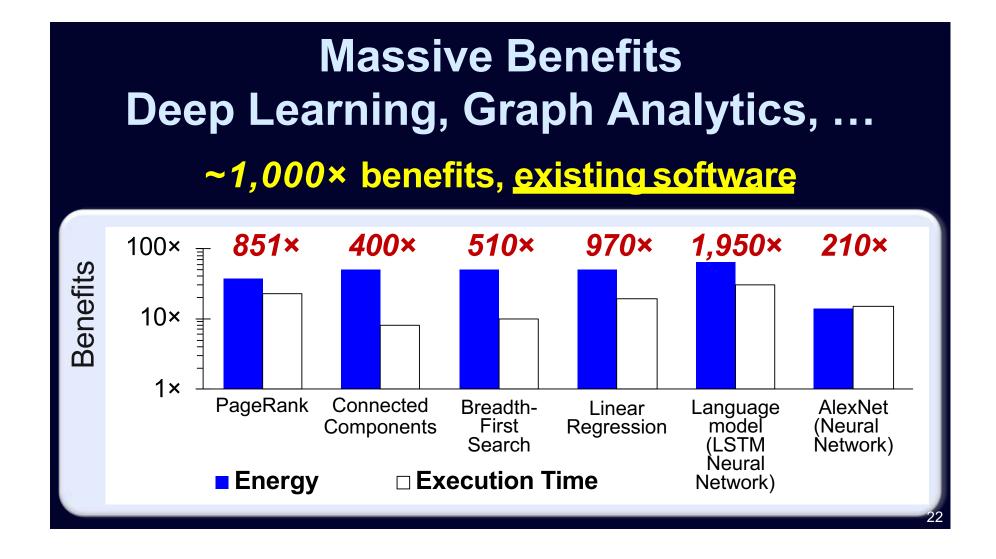

# **Application Challenges**

#### Abundant-data apps.

Brain-inspired  $\supset$  Neural Nets

#### **Chip realization ?**

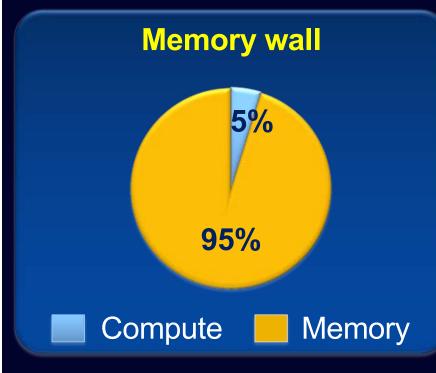

- Compute + memory

- Dense connectivity

- Energy efficiency

#### • Footprint

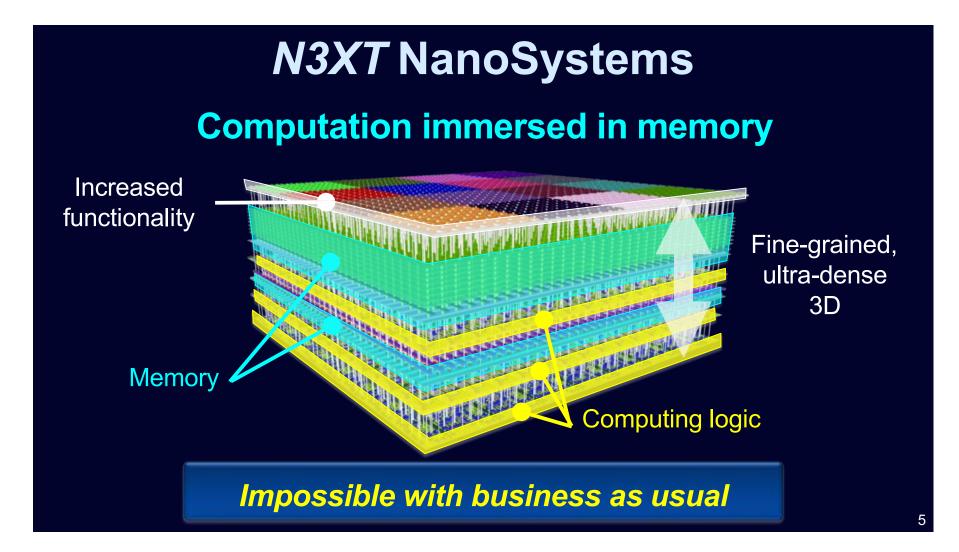

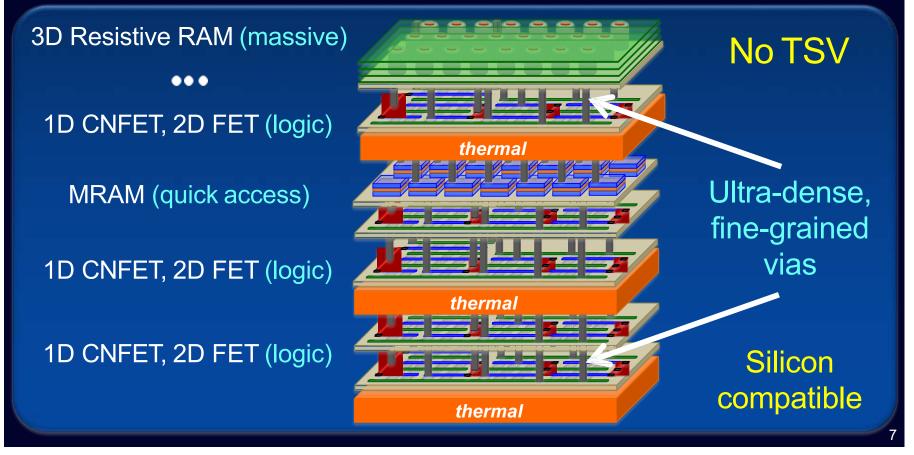

# **N3XT** NanoSystems

### **Computation immersed in memory**

# Nano-Engineered Computing Systems Technology

#### INVITED

#### The N3XT Approach to Energy-Efficient Abundant-Data Computing

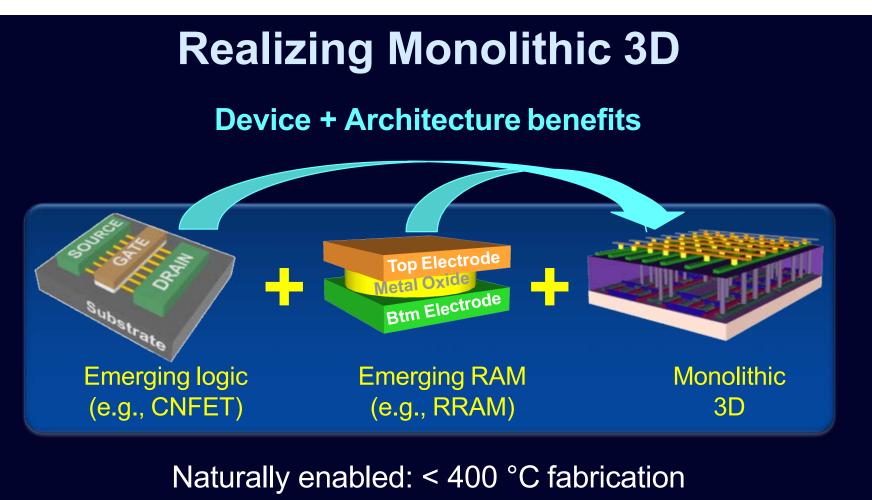

This paper enables energy-efficient computing for transformative abundant-data applications through heterogeneous integration of energy-efficient logic devices immersed in dense nonvolatile memory, with fine-grained connectivity in a monolithic 3-D architecture.

[Aly IEEE Computer 15, Proc. IEEE 19] Stanford + CMU + MIT + NTU Singapore + UC Berkeley + U. Michigan

# **N3XT** Computation Immersed in Memory

# **DARPA 3DSoC Program**

Subhasish Mitra H.-S. Philip Wong, Simon S. Wong

Nan<sup>\*</sup>Integris

Max Shulaker Anantha Chandrakasan

Brad Ferguson Mark Nelson

**Jefford Humes**

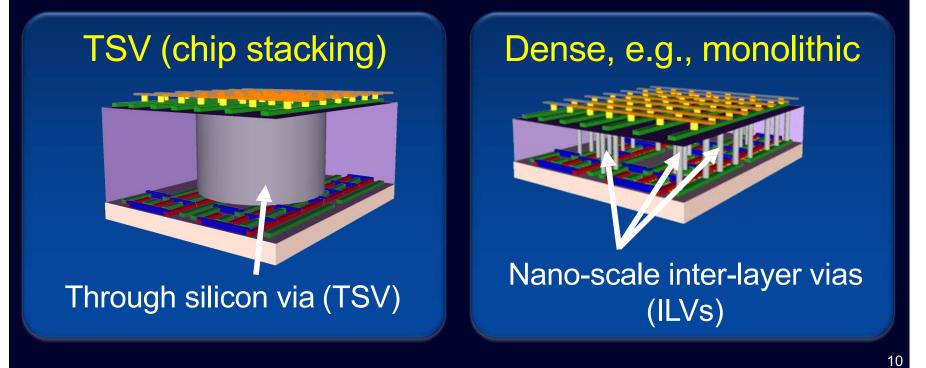

# **3D Integration**

#### Massive ILV density >> TSV density

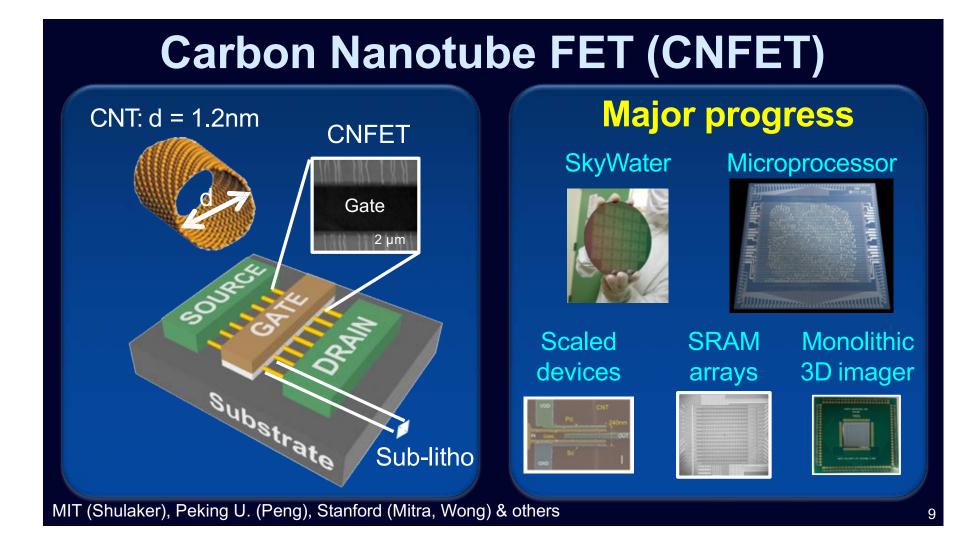

# Foundry CNFET + RRAM + Monolithic 3D

#### First 3D Nanotube and RRAM ICs Come Out of Foundry

SkyWater Technology Foundry produces first wafers in a drive to match performance of cutting-edge silicon chips

#

By Samuel K. Moore

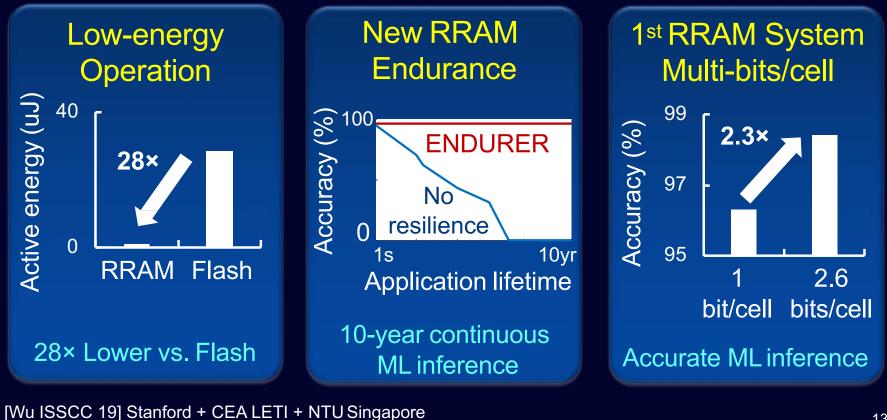

## **RRAM Advances**

# First Multiple bits-per-cell RRAM System

|                               | Bits<br>per cell | Cells<br>measured                           | Neural nets<br>Optimized weight encoding               |

|-------------------------------|------------------|---------------------------------------------|--------------------------------------------------------|

| Our work<br>new<br>algorithms | 3                | Full arrays                                 | T Cross-layer<br>RRAM arrays<br>multiple bits-per-cell |

| <b>Prior work</b><br>ad hoc   | 2-6.5            | Single cell,<br>few<br>hand-picked<br>cells | 2.3× accurate inference<br>Same hardware, bigger model |

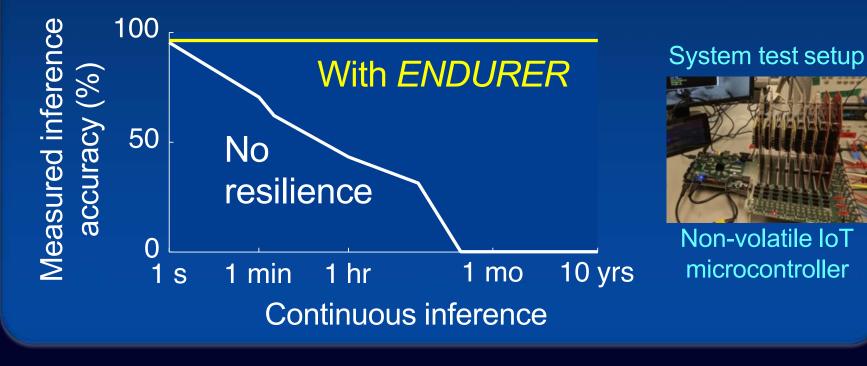

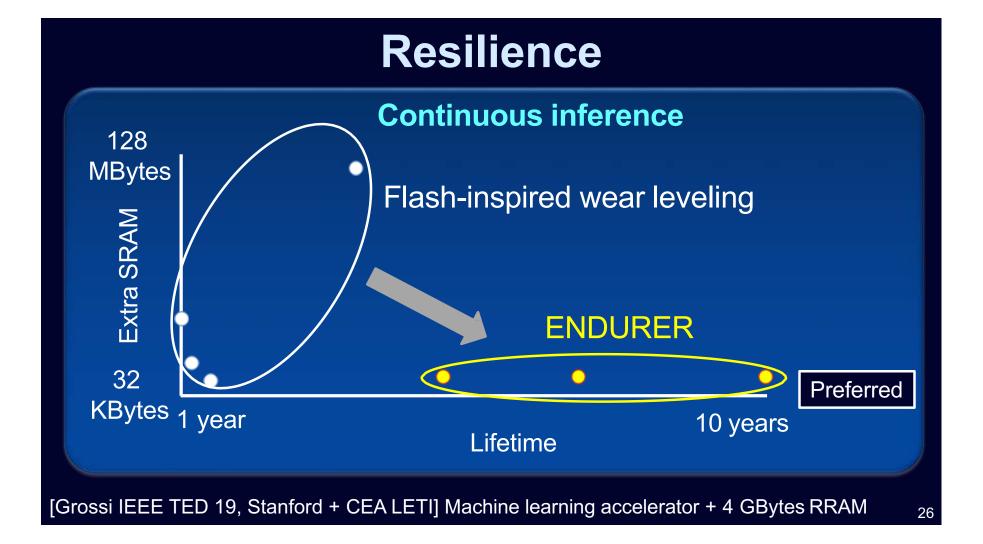

# ENDURER

### 10-year lifetime (measured)

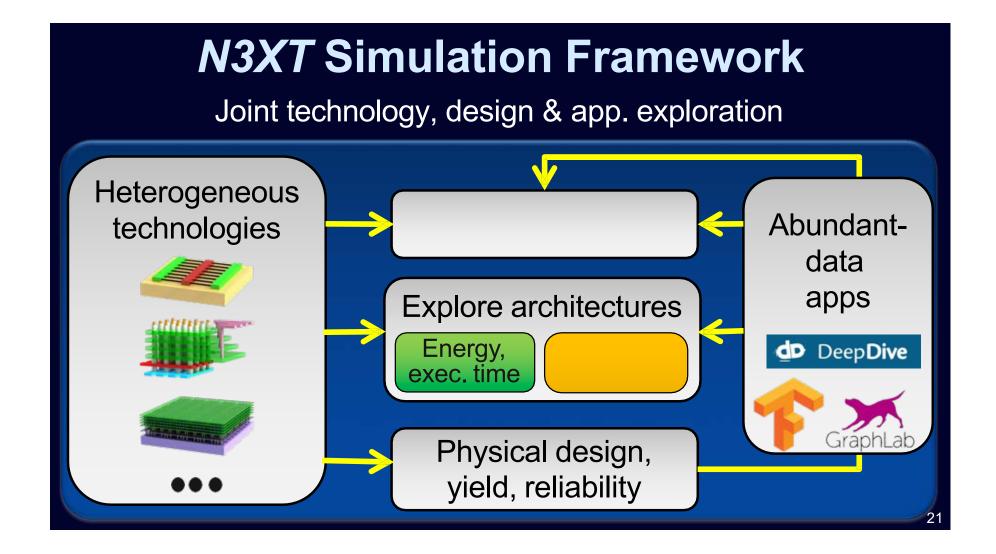

# **N3XT** Cross-Layer ModSim

Many chips system

Few chips system

Architecture

Circuit

Device

## Many FAQs Answered

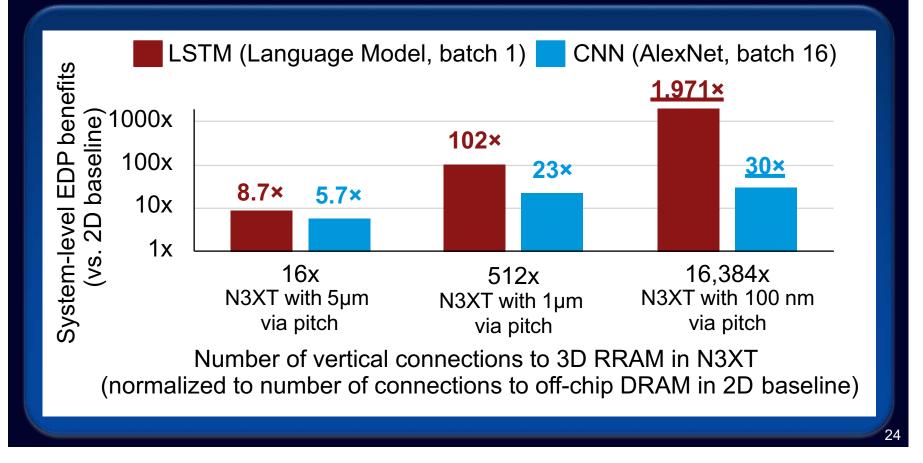

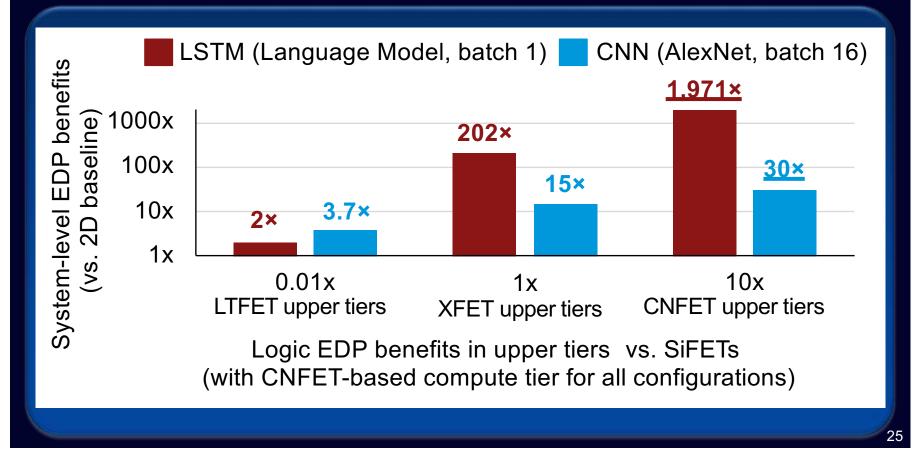

- 1. Where do benefits come from ?

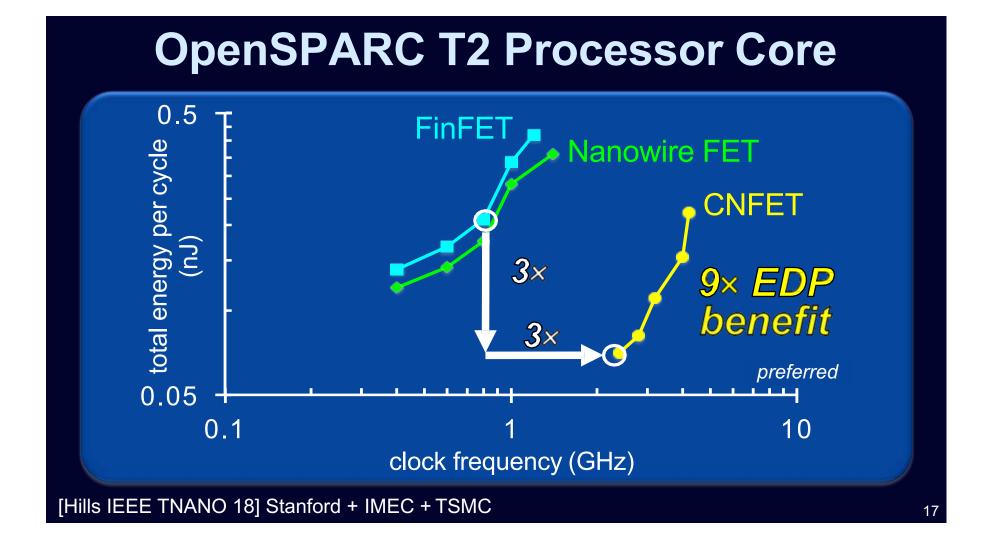

- 2. Wires limit performance ? Why research FETs ?

- **3**. CNFET contact resistance ?

- 4. Aren't FETs good enough already ?

- **5**. CNT variations ?

# NanoSystem Design Kit

# **N3XT** Cross-Layer ModSim

Many chips system

**Few chips system**

Architecture

Circuit

Device

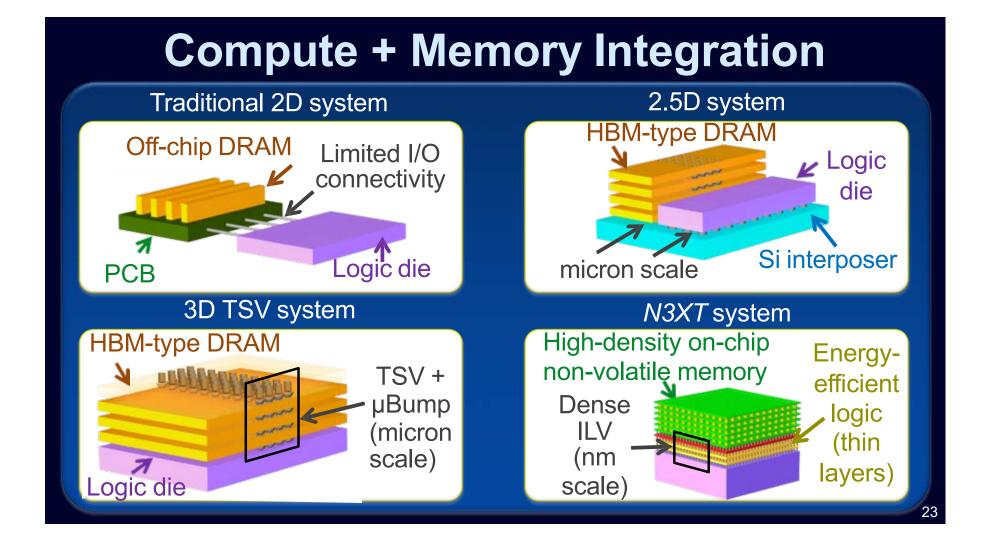

# **Compute + Memory Integration**

# **Compute + Memory Integration**

# Many More (ModSim) Opportunities

- Software mapping

- New micro-architectures & memory hierarchy

- I Dense compute + thermal

# **N3XT** Cross-Layer ModSim

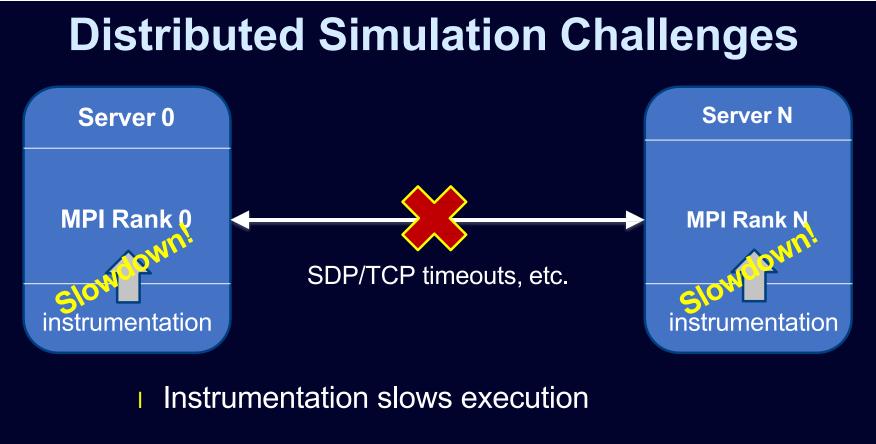

Remote nodes can't reply before timeout

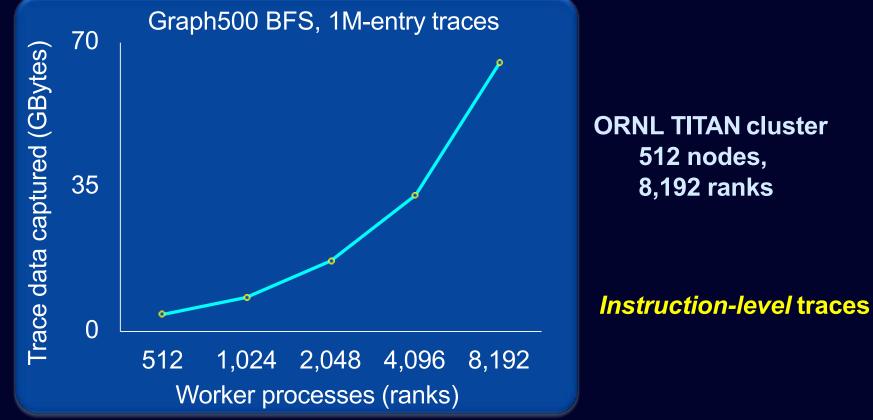

# **Ongoing: Decoupled Tracing + ModSim**

30

# Thanks: Students, Sponsors, Collaborators

## Conclusion

NanoSystems today

RRAM, CNFET, dense (monolithic) 3D

In fabs now (from labs)

Many cross-layer opportunities